基于xilinx平台的FPGA开发流程

初学FPGA时我应该学什么

作为刚开始学习FPGA的开发目标是根据设计需求,写verilog代码,使之能够在指定的开发平台上实现相应的功能。在最开始的学习过程中,有几个点应该着重学习:

- 开发和调试(怎么写代码以及出了问题怎么分析、调整)

- Verilog语法

- 开发工具的使用——vivado

- 仿真工具的使用——modsim,在数字电路中,仿真基本接近真实情况,具有可信度!

- 高、低速场景接口逻辑设计,即保证数据在不同模块之间的正确传输

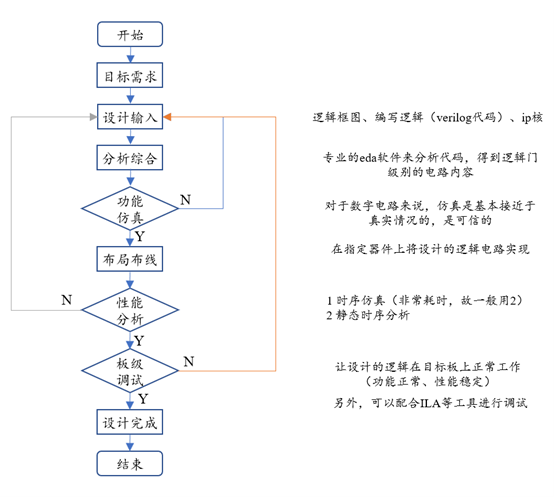

FPGA开发流程

围绕着“根据预期目标写代码,调试功能及性能,最终上板运行”的思路,一般的开发思路,如下

性能分析主要就是时序方面仿真分析,一般有时序仿真(非常耗时)和静态时序分析两种方式,在实际开发过程中,一般用到静态时序分析。

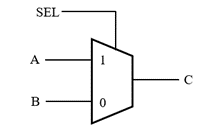

接下来,以二选一多路选择器项目为例,介绍一下如何在vivado软件平台的开发流程具体是怎么样的。选择器的输出由3个输入的状态决定,即这个小的试验目标可以是在用3个按键作为输入,一个led灯作为输出,实现led的亮灭控制是A、B哪个按键决定的功能。

在vivado软件中,对应流程的操作如下:

创建工程 Create Project

设计输入 Add Sources——Add or create design sources

分析综合 Run Synthesis

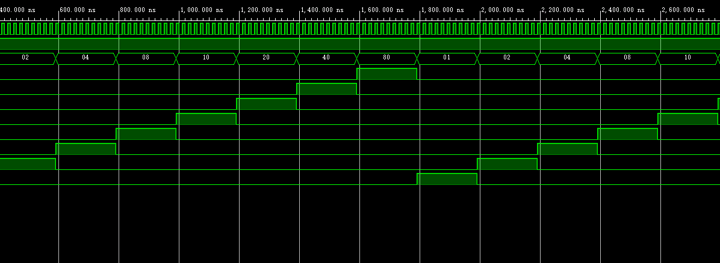

仿真 Add Sources——Add or create simulation sources

布局布线 Run Implementation

性能分析 Run Post-Implementation Timing Simulation

上板验证

下面有几点需要注意一下:

创建工程过程中,注意一下器件选择,器件型号可以在开发版fpga芯片上读出来,速度等级需要查看相关配套资料,且数字越大,运行速度越快。

仿真代码testbench的“结构”基本如下,对于vivado自带的仿真工具,如果仿真时间没跑完需要手动点击,`Run All``。

1 | `timescale 1ns/1ns |

上板验证,在左侧导航栏点开SYNTHESIS——Open Syntheszed Design,打开layout——io planning进行配置,需要配置每个端口位置以及端口电平标准,配置好之后ctrl+s保存为xdc文件,在sources中可以看到。最后,生成bit流文件,Open Hardware Manager连接到开发板——右键开发板型号(Program device),下载程序进行调试。

总结

作为FPGA学习的最初阶段,主要介绍了一下应该需要注意学习那些内容,其次了解并熟悉基本的开发流程,以及基于vivado开发时具体每一步应该怎么操作。